big Navi泄露? RX 5950 XT显卡24GB HBM2e爆料太假了

不出意外的话,3月初的财务分析师会议会上AMD就会宣布RDNA2代GPU架构,不仅支持硬件光追,而且规模更大,传闻中big Navi大核心性能可超越RTX 2080 Ti,有可能命名为RX 5950 XT显卡。

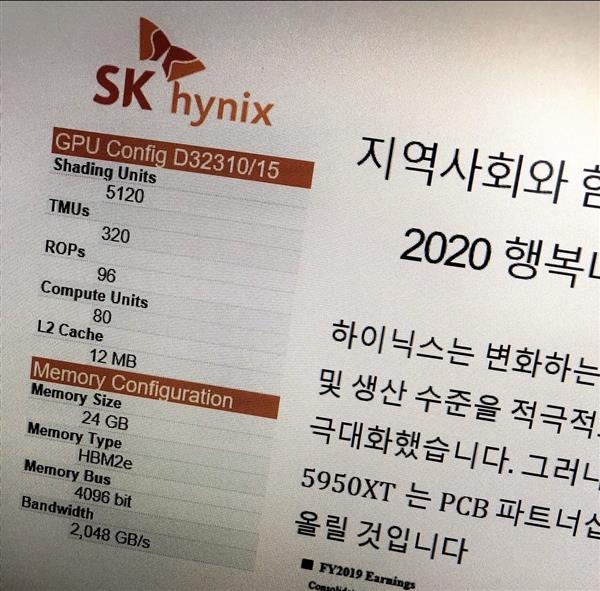

日前还有更详细的规格泄露,有SK海力士员工泄露了D32310/15的部分参数,GPU包括80组CU、5120个流处理器,320个TMU(纹理单元)、96个ROP光栅单元,二级缓存12MB。

显存方面,24GB HBM2E,4096bit,带宽高达2TB/s(针脚带宽4Gbps)。

这个传闻这两天引发了国内外A饭的热议,不过SK海力士方面已经辟谣了,否认发表过相关爆料,要求停止传播这一谣言。

SK海力士的辟谣没完全消除大家的“误解”,因为上面那个爆料看起来很准确,很多人还是深信不疑,毕竟这个爆料显示出big Navi真的是很好很强大。

那就是专业角度来辟谣吧,hardwaretimes网站发文分析了爆料中的big Navi显卡的规格出,认为有三处是不可能的:

第一,24GB HBM2e、2048GB/s的显存配置是不可能的。HBM2e显存虽然可以做到12-hi堆栈,但普通是8-hi堆栈,每个HBM2e芯片的等位位宽是1024bit,每个芯片核心容量16Gbit,总堆栈16GB,1.2GHz等效频率下带宽410GB/s。

如果是2个芯片堆栈一组,那么速率3.2Gbps,总容量32GB,每通道位宽2048bit。

再来看上面的爆料,24GB HBM2e显存意味着等效位宽1536bit,很诡异,而且带宽还达到了2048GB/s,这也是不可能的,每个HBM2e的带宽只有410GB/s,2组也不超过1024GB/s。

第二个疑点是ROP光栅单元,爆料称它是96组ROP,但RX 5700 XT中是64组ROP,big Navi说是2倍规模,那ROP单元应该是128个才对。

理论上来说,96组ROP单元也不是绝对不可能出现,这时候内存控制器就是混合的、不对等的。

还有就是L2缓存容量,爆料显示是12MB L2缓存,这是RX 5700 XT的3倍,但如果CU单元只是翻倍,那应该是8MB L2缓存才合理,除非AMD在RDNA 2架构中改变了L2缓存配置。

总之,不论从哪一方面来看,这次爆料big Navi核心的规格都不太合理,漏洞很多,再加上SK海力士的辟谣,这次的泄漏大概率是假的。