AMD Zen3架构第三代霄龙曝光:单芯片集成15个Die

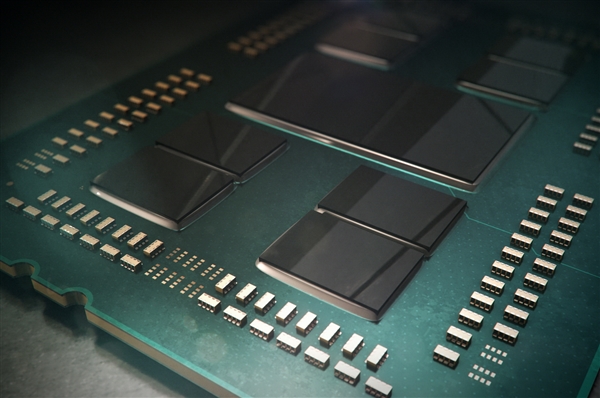

AMD不久前刚刚发布了代号Rome(罗马)第二代EPYC霄龙处理器,拥有7nm工艺和Zen 2架构,而且采用了chiplet小芯片设计,集成最多八个CPU Die和一个IO Die设计非常独特。

根据规划,接下来将有第三代Milan(米兰),7nm+工艺、Zen 3架构,再往后是第四代Genoa(热那亚),Zen 4架构。

据最新曝料,AMD Milan内部将集成最多15个Die,比现在多出来6个。

其中一个肯定还是IO Die,但剩下的14个不可能全是CPU,因为八通道DDR4内存的带宽只能支持最多10个CPU Die(最多80个核心),这就意味着最多8个或者10个CPU Die。——当然内存通道超过八个的可能性微乎其微。

剩下的6个或4个Die会是什么呢?目测极有可能是HBM高带宽显存,通过中介层(Interposer)与CPU Die直接互连,提供远胜于DDR4内存的高带宽、低延迟,彻底消除瓶颈。

这样的话,Milan的配置可能会是10+4+1或者8+6+1。

不过之前有说法称Milan仍然是8+1配置,那可能是不同的版本。

标签: AMD Zen3第三代霄龙

相关阅读

评论

精彩评论